# A Numerical Engine for Distributed Sparse Matrices

by

# Ricardo Telichevesky

B.Sc., Universidade Federal do Rio Grande do Sul (1985) M.Sc., The Technion - Israel Institute of Technology (1988)

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

at the

### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

January 1994

© 1994 Massachusetts Institute of Technology All rights reserved

Signature of Author\_\_\_\_

Department of Electrical Engineering and Computer Science

Certified by\_\_\_\_\_

Jacob K. White, Associate Professor of Electrical Engineering Thesis Advisor

Certified by\_\_\_\_

William J. Dally, Associate Professor of Computer Science and Engineering Thesis Advisor

Accepted by\_\_\_\_

Frederic R. Morgenthaler, Professor of Electrical Engineering Chairman, Department Committee on Graduate Students

# A Numerical Engine for Distributed Sparse Matrices

by

Ricardo Telichevesky

Submitted to the Department of Electrical Engineering and Computer Science on August 11, 2000, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

#### Abstract

In fields as diverse as electronic circuit design, fluid dynamics, and structural analysis, the behavior of complex systems is modeled by large, sparsely coupled systems of differential equations. Numerical solution of such systems is computationally expensive because even the most efficient algorithms evaluate and factor large sparse matrices hundreds or thousands of times, and on most general purpose computers sparse matrix operations are inefficient. Part of the problem is that accessing sparse matrix elements is complicated, resulting in a poor utilization of computational resources. The irregular non-zero pattern makes it very difficult to parallelize the operations; and the non-uniform data access time makes pipelining very inefficient.

This thesis suggests exploiting the infrequent change in matrix structure by developing a symbolic compiler, and a special purpose parallel computer that uses compiler clues to accelerate sparse data access. The compiler combines partitioning, scheduling, and storage allocation algorithms in order to exploit locality of reference, achieve a high degree of parallelism, and simplify the operand access in the sparse matrix, which in turn insures efficient pipelining. Each processing element contains a specialized datapath consisting of multiple interleaved memories and functional units, and a microprogrammed control unit capable of initiating several datapath operations per clock cycle. Extensive behavioral and register transfer level (RTL) emulation of the execution of SIMLAB, a circuit simulation program, suggests that the combination of these hardware and software techniques yield a high degree of utilization of computational resources both in the assembly of circuit equations using device models and in its associated sparse matrix solution.

Thesis Supervisors: Jacob K. White, Associate Professor of Electrical Engineering

William J. Dally, Associate Professor of Computer Science and Engineering

# Acknowledgments

This thesis is based on work supported in part by the Conselho Nacional de Desenvolvimento Científico e Tecnológico (CNPq-Brazil) and the Office of Naval Research.

This thesis results from a combined effort with Professors Jacob White and William Dally. More than providing advice, support, and guidance, their ideas are an essential part of this research.

I wish to thank all the members of the research group that have helped me in this research. Miguel Silveira, Keith Nabors, Kevin Lam, Khalid Rahmat, and Don Baltus are notable collaborators in the actual implementation of the algorithms presented in this thesis, as well as in the architectural design. Steven McCormick provided the essential macros that helped so much in writing the thesis. Bob Armstrong, our UNIX guru, was always there to answer all sorts of system-related questions.

Prathima Agrawal and John Trotter of AT&T Bell Labs have been involved in the early stages of this research and contributed significantly to the development of scheduling and partitioning heuristics. Greg Papadopoulos also took time to participate on my thesis committee. Milena Levak helped so much in all the complicated requirements of the International Students Office. Many thanks to Marilyn Pierce, a saint that by saying "No problem" miraculously keeps the sanity of graduate students.

Thanks to José Monteiro, Mattan Kamon, Ignacio McQuirk, Filip Van Aelten, Songmin Kim, Jennifer Lloyd, Xuejun Cai, Stan Liao, Amelia Shen, Chris Umminger, Joel Phillips, and all people in the eighth floor for their invaluable assistance.

Thanks to my friends Rodrigo Paiva, Julia Allen, Cristina Lopes, Brian Pan, Chris Berry, and Paul Yu for the encouragement, patience and help in so many aspects of my graduate student life here in the United States. From Brazil, the encouragement and emotional support of my long-time friends Ricardo Mester, Jairo Moscovich, Nelson Zamel and of my family made it all possible.

# Contents

| 1 | Intr | coduction                                                      | 15 |

|---|------|----------------------------------------------------------------|----|

|   | 1.1  | Thesis Contributions                                           | 15 |

|   | 1.2  | Numerical Solution of Differential Equations                   | 17 |

|   | 1.3  | Parallel Sparse Matrix Decomposition                           | 19 |

|   |      | 1.3.1 Reordering                                               | 19 |

|   |      | 1.3.2 Storage Organization                                     | 20 |

|   |      | 1.3.3 Scheduling                                               | 21 |

|   | 1.4  | Parallel Circuit Simulation                                    | 22 |

|   | 1.5  | Numerical Engine Architecture                                  | 23 |

|   |      | 1.5.1 Related Work                                             | 24 |

|   | 1.6  | Thesis Outline                                                 | 25 |

|   | _    |                                                                | _  |

| 2 |      | r r                                                            | 27 |

|   | 2.1  | 1                                                              | 29 |

|   | 2.2  | The YSMP Scatter-Gather Approach                               | 32 |

|   |      | 2.2.1 Efficient Interleaving in Scattered Vectors              | 35 |

|   |      | 2.2.2 A Scatter-Gather Special Purpose Processor               | 38 |

|   | 2.3  | Scheduling Heuristics for Fast Sparse Matrix Decomposition     | 40 |

|   |      | 2.3.1 Background                                               | 40 |

|   |      | 2.3.2 Partitioning Schemes                                     | 44 |

|   |      | 2.3.3 Scheduling Schemes                                       | 46 |

|   |      | 2.3.4 Scheduling Results                                       | 52 |

|   | 2.4  | Overlapped-Scattered Arrays for Sparse Matrix Factorization    | 54 |

|   |      | 2.4.1 OSA Overhead Costs                                       | 56 |

|   |      | 2.4.2 OSA-Based Fast Sparse Matrix Package                     | 57 |

|   |      | 2.4.3 OSA-Based Fast Sparse Matrix Decomposition Hardware      | 59 |

|   | 2.5  | Overlapped-Overlapped Scattered Arrays                         | 62 |

|   |      | 2.5.1 $O^2SA$ Performance                                      | 63 |

|   |      | 2.5.2 $O^2SA$ -Based Fast Sparse Matrix Decomposition Hardware | 64 |

|              |      | 2.5.3 Scheduling for $O^2SA$                                                | 7 |  |  |  |  |  |  |  |  |

|--------------|------|-----------------------------------------------------------------------------|---|--|--|--|--|--|--|--|--|

|              | 2.6  | Implementation Issues for Parallel Sparse Matrix Factorization on a General |   |  |  |  |  |  |  |  |  |

|              |      | Purpose Multiprocessor                                                      | 0 |  |  |  |  |  |  |  |  |

|              |      | 2.6.1 Influence of Hardware Parameters on Multiprocessor Performance 7      | 0 |  |  |  |  |  |  |  |  |

|              |      | 2.6.2 Scheduler Validation                                                  | 2 |  |  |  |  |  |  |  |  |

| 3            | Par  | allel Circuit Simulation 7'                                                 | 7 |  |  |  |  |  |  |  |  |

|              | 3.1  | Major Issues in Parallel Circuit Simulation                                 | 7 |  |  |  |  |  |  |  |  |

|              |      | 3.1.1 Circuit Simulation Background                                         | 7 |  |  |  |  |  |  |  |  |

|              |      | 3.1.2 Overview of the Parallel Circuit Simulation Process                   | 2 |  |  |  |  |  |  |  |  |

|              | 3.2  | Parallel Model Evaluation                                                   | 5 |  |  |  |  |  |  |  |  |

|              |      | 3.2.1 Linear Elements and Voltage Sources                                   | 5 |  |  |  |  |  |  |  |  |

|              |      | 3.2.2 Parallel Evaluation of Non-Linear Elements                            | 9 |  |  |  |  |  |  |  |  |

|              | 3.3  | Device Evaluation and Contribution Stamping Multiprocessor Performance 9    | 2 |  |  |  |  |  |  |  |  |

| 4            | Nur  | nerical Engine Architecture 9'                                              | 7 |  |  |  |  |  |  |  |  |

|              | 4.1  | System Considerations                                                       | 8 |  |  |  |  |  |  |  |  |

|              |      | 4.1.1 Timing Conventions                                                    | 8 |  |  |  |  |  |  |  |  |

|              |      | 4.1.2 Interconnection Network                                               | 0 |  |  |  |  |  |  |  |  |

|              | 4.2  | Processing Element Architecture                                             | 4 |  |  |  |  |  |  |  |  |

|              |      | 4.2.1 Overview                                                              | 4 |  |  |  |  |  |  |  |  |

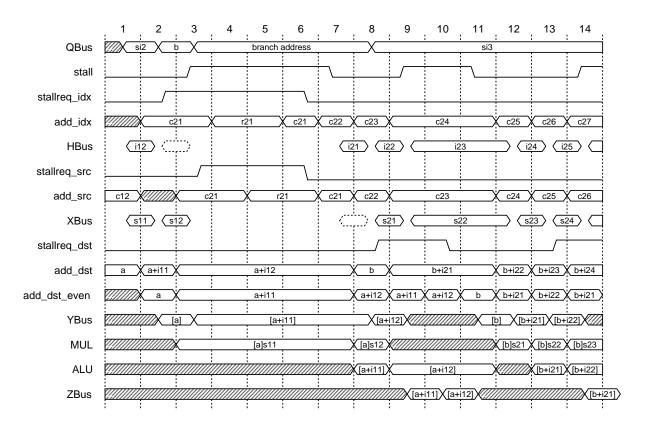

|              |      | 4.2.2 Pipelined Operation and Stall Issues                                  | 8 |  |  |  |  |  |  |  |  |

|              |      | 4.2.3 Floating Point Subsystem                                              | 1 |  |  |  |  |  |  |  |  |

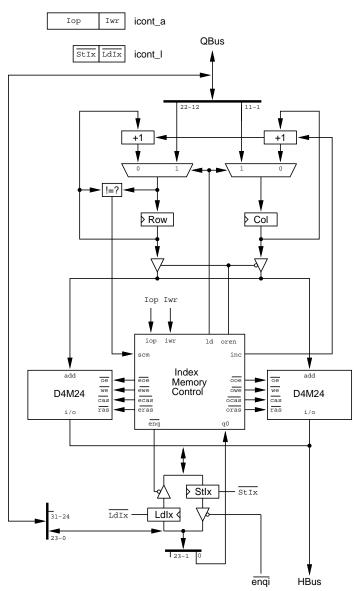

|              |      | 4.2.4 Memory System                                                         | 8 |  |  |  |  |  |  |  |  |

|              |      | 4.2.5 Network Interface                                                     | 4 |  |  |  |  |  |  |  |  |

|              |      | 4.2.6 Microprogrammed Controller                                            | 8 |  |  |  |  |  |  |  |  |

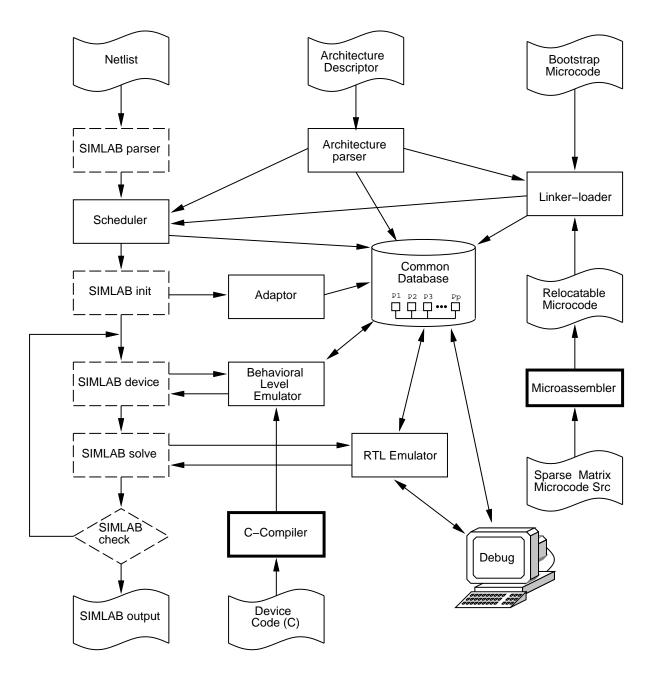

|              | 4.3  | Architecture Emulation                                                      | 6 |  |  |  |  |  |  |  |  |

|              |      | 4.3.1 Behavioral Level Emulation                                            | 6 |  |  |  |  |  |  |  |  |

|              |      | 4.3.2 RTL Emulation                                                         | 7 |  |  |  |  |  |  |  |  |

|              | 4.4  | Architecture Emulation Results                                              | 9 |  |  |  |  |  |  |  |  |

| 5            | Con  | clusion and Future Work 153                                                 | 3 |  |  |  |  |  |  |  |  |

|              | 5.1  | Major Contributions                                                         | 3 |  |  |  |  |  |  |  |  |

|              | 5.2  | Future Work                                                                 | 4 |  |  |  |  |  |  |  |  |

| $\mathbf{A}$ | Fast | Evaluation of Transcendental Functions 15'                                  | 7 |  |  |  |  |  |  |  |  |

|              | A.1  | A.1 Background                                                              |   |  |  |  |  |  |  |  |  |

|              | A.2  | Evaluation of Transcendental Functions in Multiple Functional Units 15      | 9 |  |  |  |  |  |  |  |  |

| в            | Em   | ulation Tools 16                                                            | 3 |  |  |  |  |  |  |  |  |

# List of Figures

| 1-1         | Introducing a symbolic precompilation step for SIMLAB                                                               | 16 |

|-------------|---------------------------------------------------------------------------------------------------------------------|----|

| 1-2         | Sparse matrix created during the simulation of the first and second stages of an                                    |    |

|             | infinite impulse response digital filter                                                                            | 18 |

| 1-3         | General architecture of the PACE                                                                                    | 25 |

| 2-1         | A sparse matrix (a) and its associated orthogonal linked list storage (b) $\ldots$ .                                | 28 |

| 2-2         | Source-row directed (a) and target-row directed (b) forms of sparse matrix de-                                      |    |

|             | composition                                                                                                         | 33 |

| 2-3         | Scatter-Gather LU decomposition                                                                                     | 34 |

| 2-4         | $M$ -way interleaved memory system $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 35 |

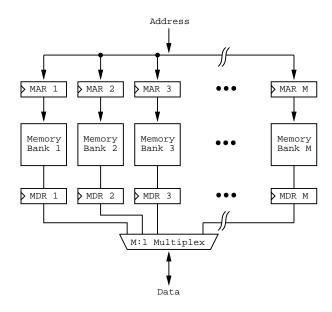

| 2-5         | Dedicated datapath for source-destination column matching                                                           | 39 |

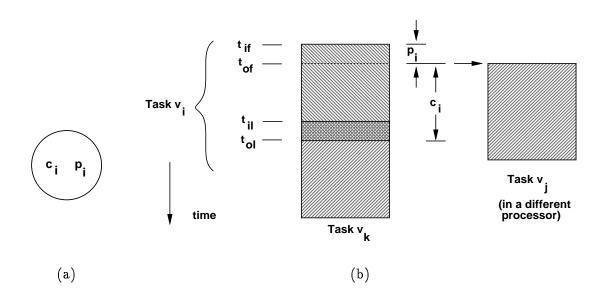

| 2-6         | Task representation and its timing                                                                                  | 42 |

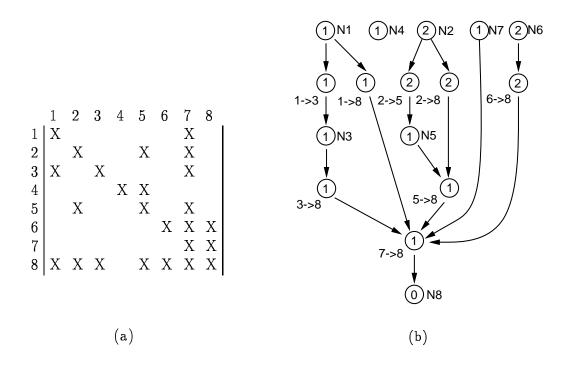

| 2-7         | A sparse matrix and its associated task graph                                                                       | 43 |

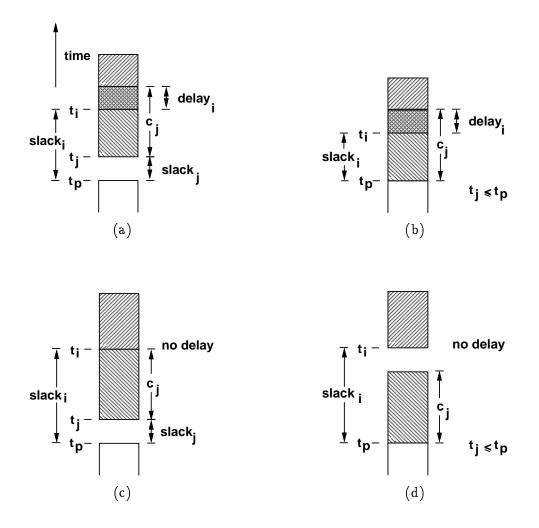

| 2-8         | Inserting a task $v_j$ before $v_i$                                                                                 | 51 |

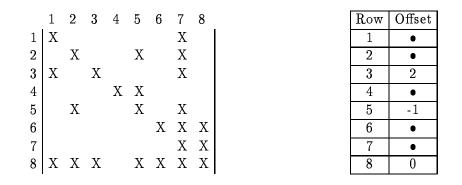

| 2-9         | Overlap-Scatter representation of a matrix                                                                          | 54 |

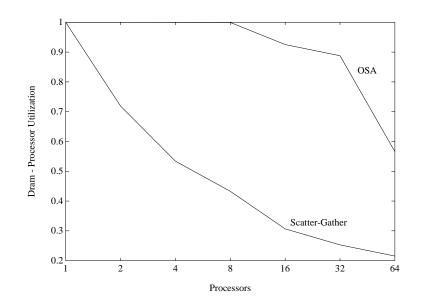

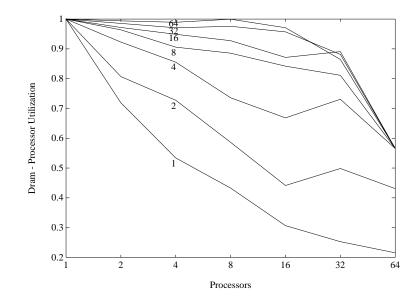

| 2-10        | Simulated processor utilization for Scatter-Gather and $OSA$ -based storage                                         | 55 |

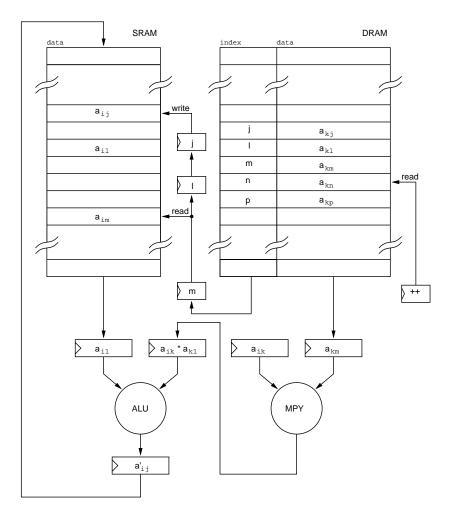

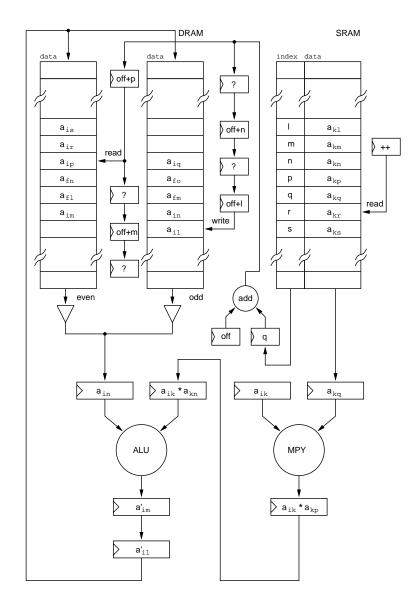

| 2-11        | Dedicated datapath for fast updates with interleaved $OSA$ access                                                   | 60 |

| 2-12        | $O^2SA$ representation of a matrix                                                                                  | 63 |

| 2-13        | Processor utilization using up to $R$ active targets on fast memory                                                 | 64 |

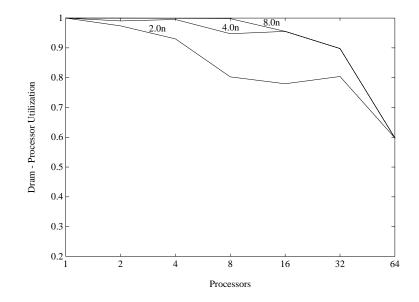

| 2-14        | Processor utilization using the $O^2SA$ structure to keep as many as possible active                                |    |

|             | targets on fast memory                                                                                              | 65 |

| 2-15        | Dedicated datapath for fast $O^2SA$ update $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$  | 66 |

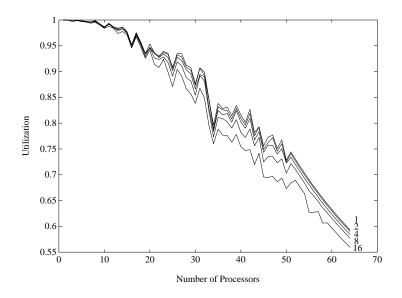

| 2-16        | Effect of the pipeline latency on system performance                                                                | 71 |

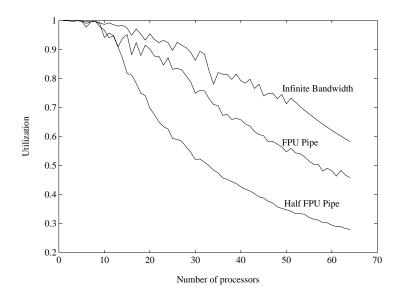

| 2-17        | Effect of the bus bandwidth on system performance                                                                   | 72 |

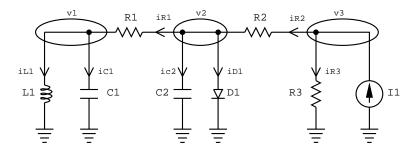

| <b>3-</b> 1 | Example circuit                                                                                                     | 78 |

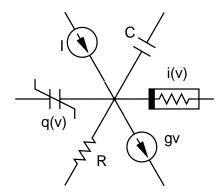

| 3-2         | Examples of elements connected to a node                                                                            | 79 |

| 3-3         | Data structures used in a multiprocessor for transient analysis of an electrical                                    |    |

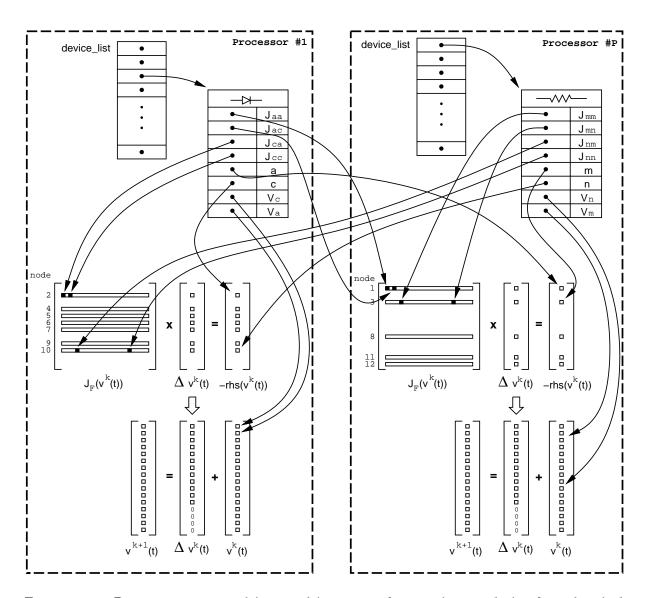

|             | circuit                                                                                                             | 83 |

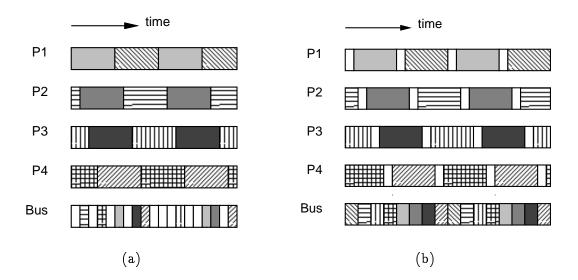

| 3-4         | Bus $slack$ (a) versus processor $idle$ (b) $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$          | 84 |

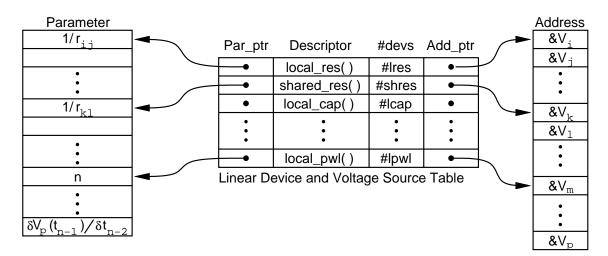

| 3-5          | Local linear device and voltage source data structures                                            |

|--------------|---------------------------------------------------------------------------------------------------|

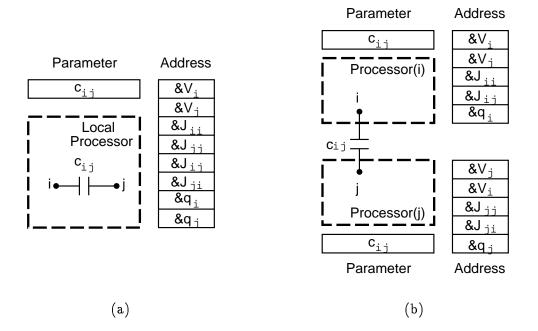

| 3-6          | Local (a) and distributed (b) capacitor evaluation and stamp data structures 86                   |

| 3-7          | Local (a) and distributed (b) independent current source evaluation and stamp                     |

|              | data structures                                                                                   |

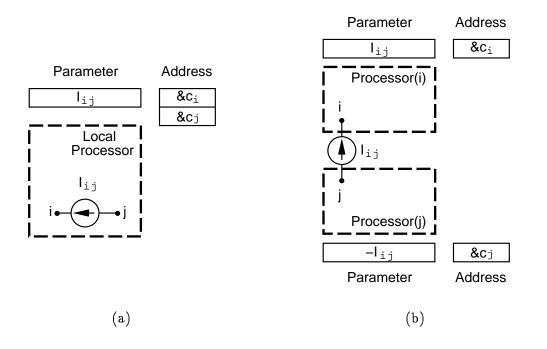

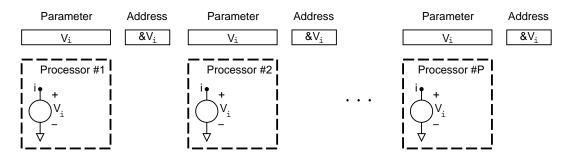

| 3-8          | Distributed independent voltage source evaluation and stamp data structures 88                    |

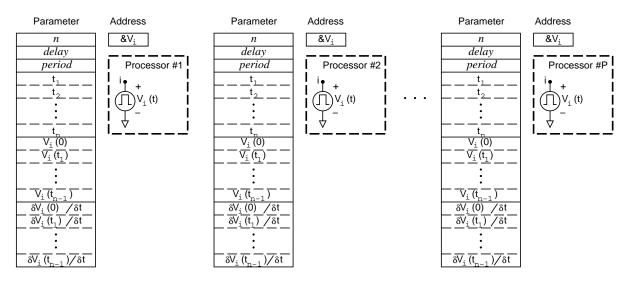

| 3-9          | Data structures for the evaluation and stamp of the independent piecewise linear                  |

|              | voltage sources                                                                                   |

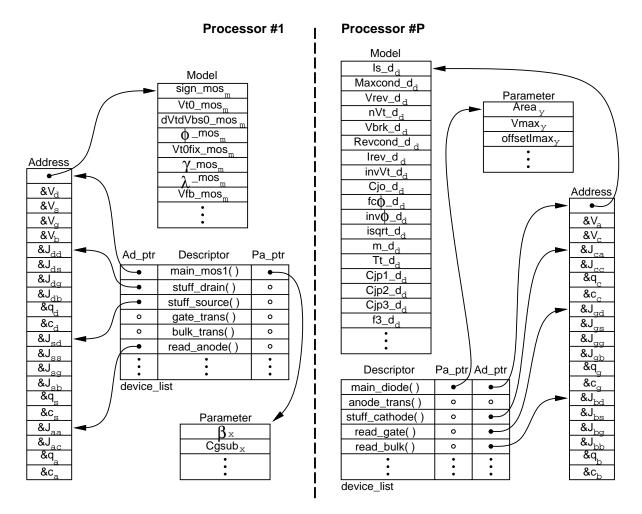

| 3-10         | Distributed non-linear device data structures                                                     |

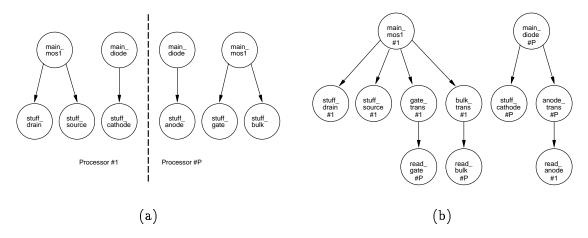

| <b>3</b> -11 | Task graphs associated with the execution of the non-linear device evaluation                     |

|              | and stamping procedures with task replication (a) and with data transmission (b) $93$             |

| 4-1          | Overview of the numerical engine architecture                                                     |

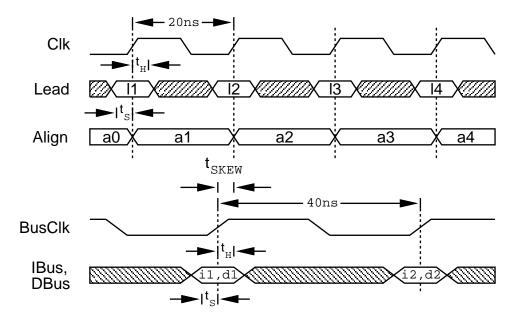

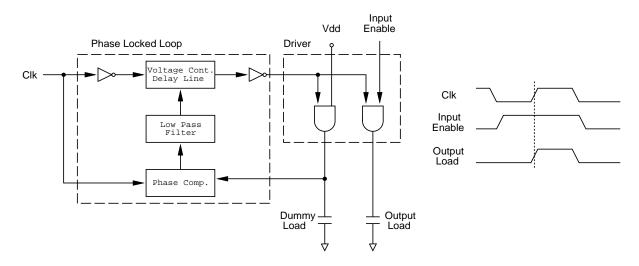

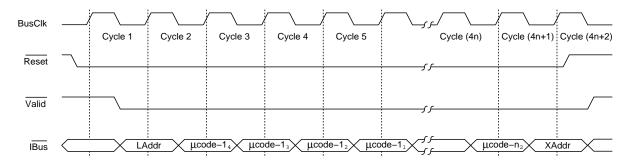

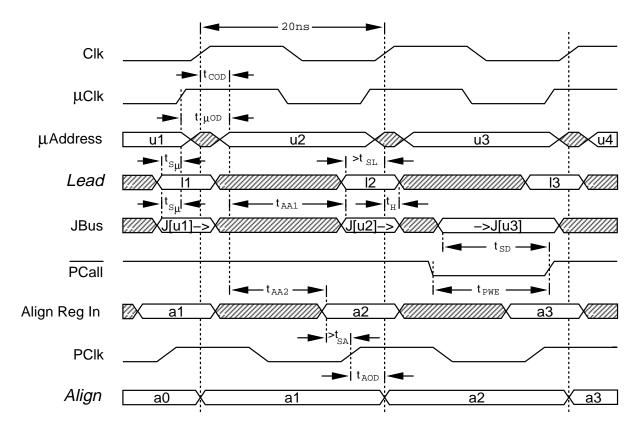

| 4-2          | Timing conventions                                                                                |

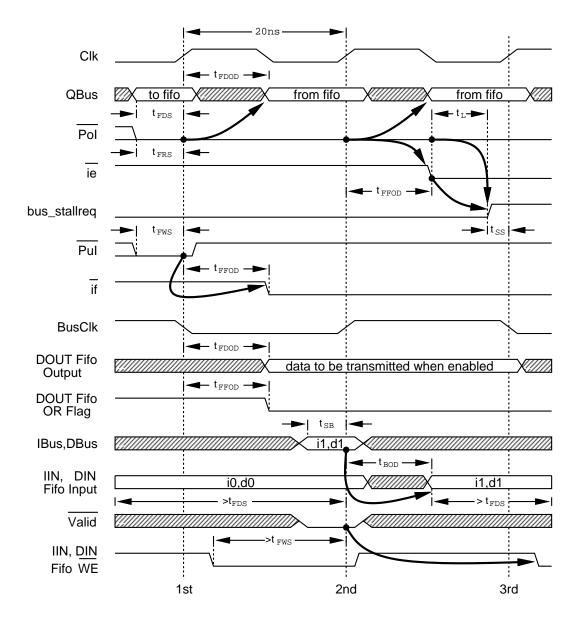

| 4-3          | Synchronization scheme for aligning arbitrary outputs with the clock input signal 100             |

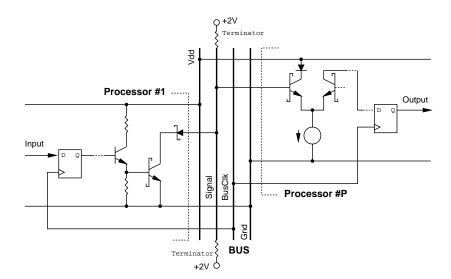

| 4-4          | A generic bus signal input and output circuits                                                    |

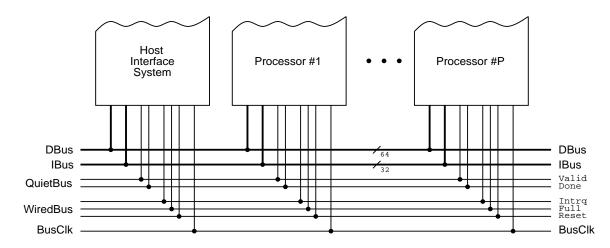

| 4-5          | Bus interface signals                                                                             |

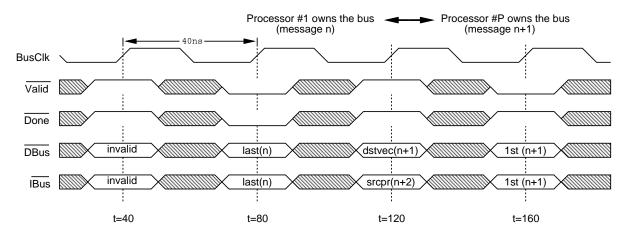

| 4-6          | Bus protocol for passing control from processor $\#1$ to processor $\#P$ 103                      |

| 4-7          | Microprogram boot sequence after reset                                                            |

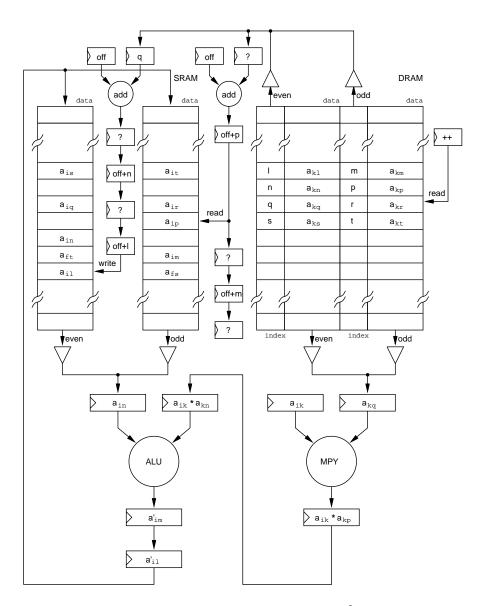

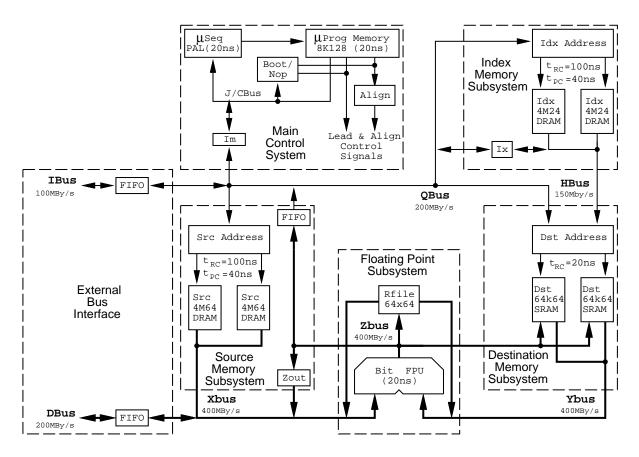

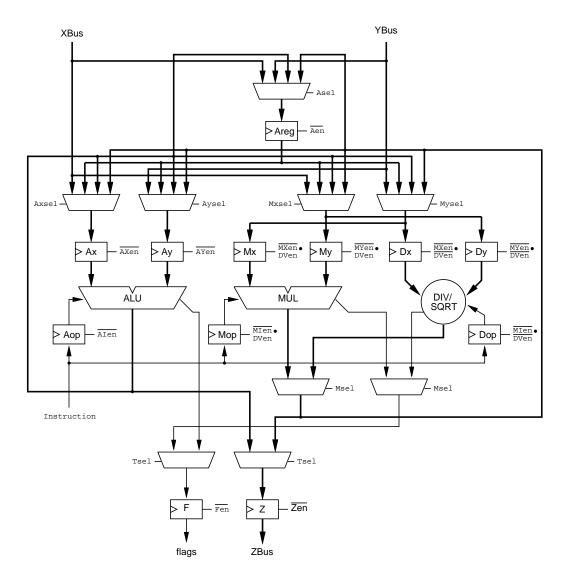

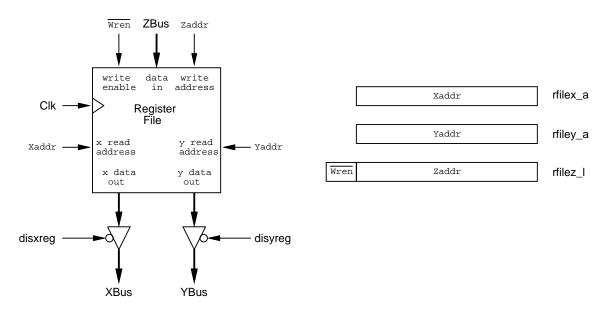

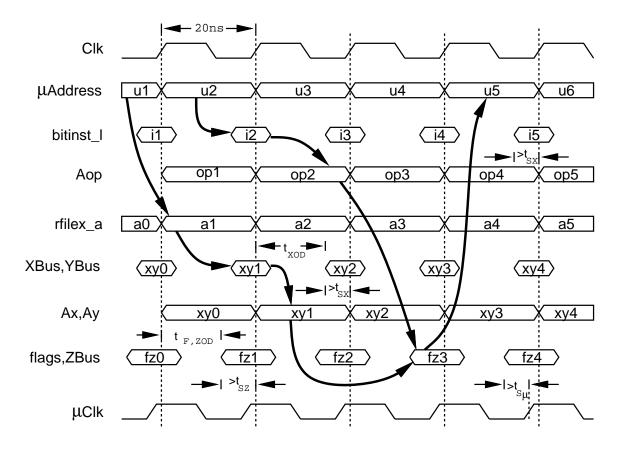

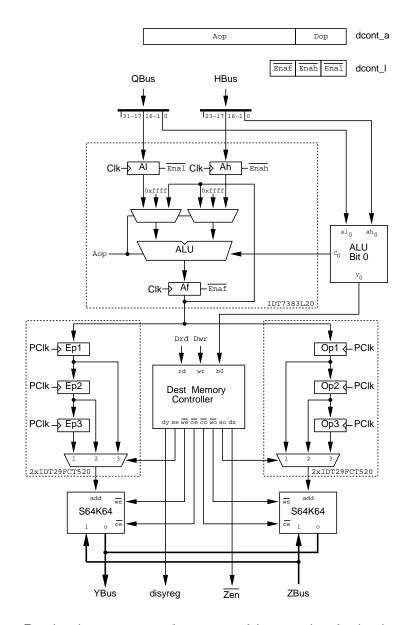

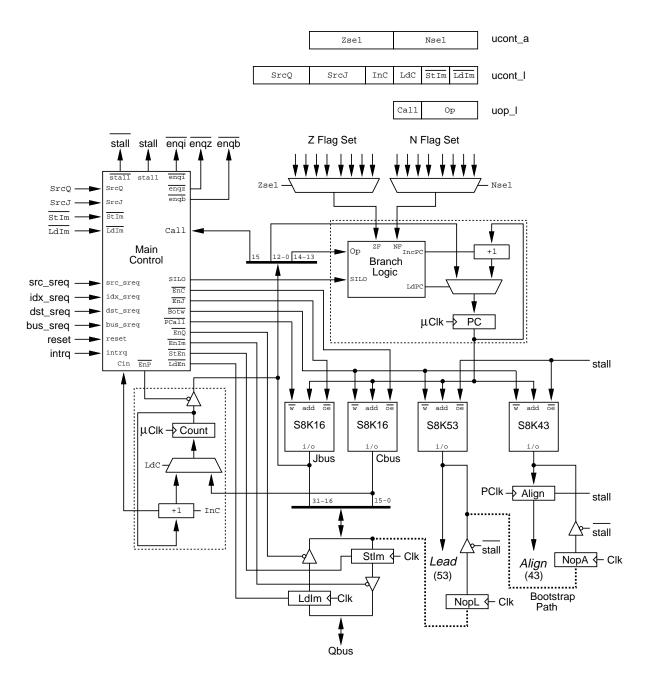

| 4-8          | Processing element internal architecture                                                          |

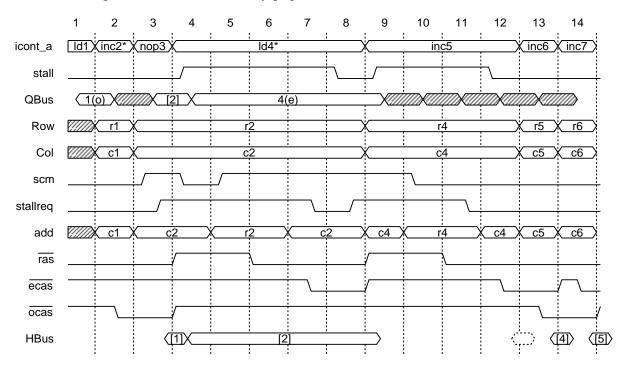

| 4-9          | Processor element pipelined operation and stall issues                                            |

| 4-10         | Floating point unit internal architecture                                                         |

| 4-11         | Floating point register file                                                                      |

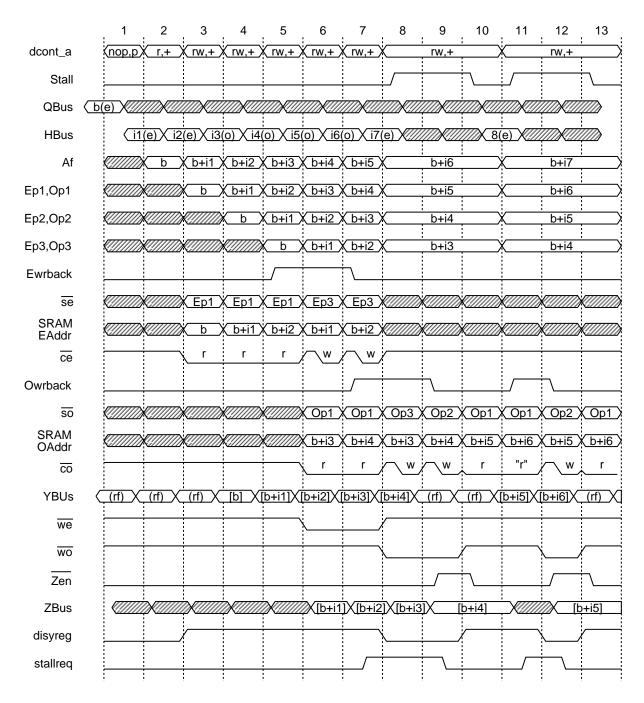

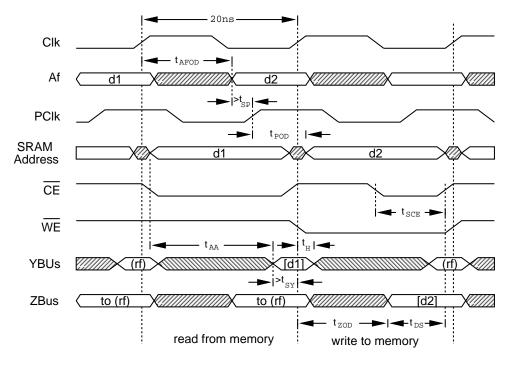

| 4-12         | Floating point unit and register file timing                                                      |

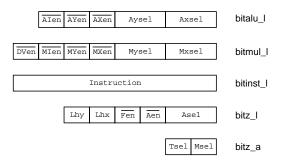

| <b>4-13</b>  | Index memory subsystem and its associated microinstruction fields                                 |

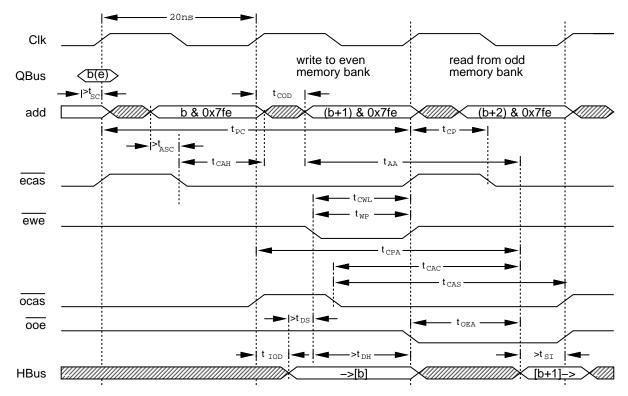

| 4-14         | A relevant sequence of operations in the index memory subsystem $\ldots \ldots \ldots \ldots 120$ |

| 4-15         | Index memory subsystem timing                                                                     |

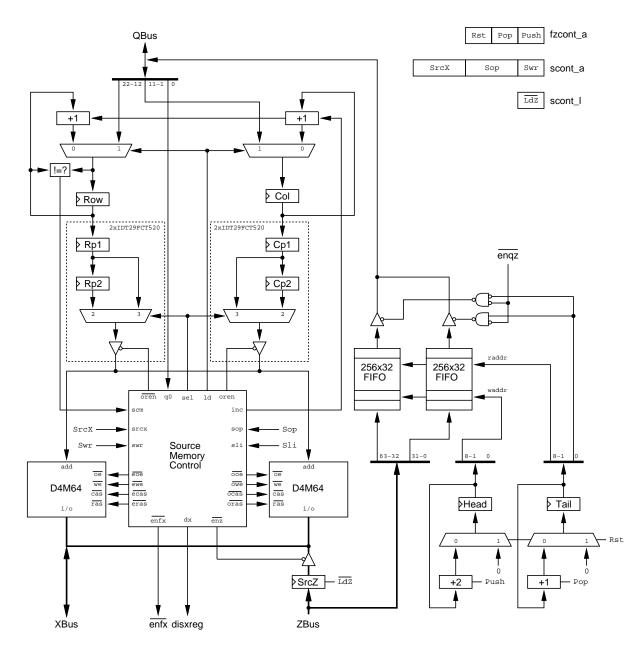

| 4-16         | Source memory subsystem and its associated microinstruction fields                                |

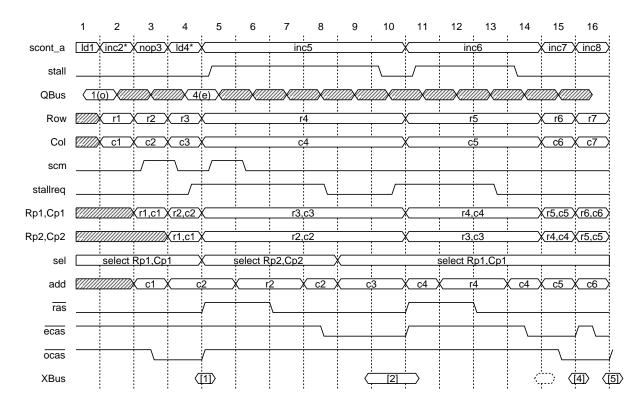

| 4-17         | A relevant sequence of operations in the source memory subsystem                                  |

| 4-18         | Destination memory subsystem and its associated microinstruction fields 129                       |

| 4-19         | A relevant sequence of operations in the destination memory subsystem $\ldots$ 131                |

| 4-20         | Destination memory subsystem timing                                                               |

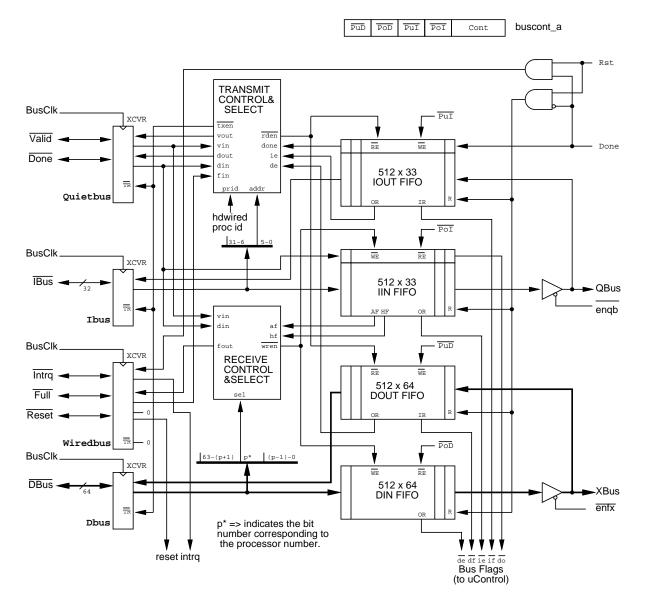

| 4-21         | Interconnection interface and its associated microinstruction fields                              |

| 4-22         | Network interface system timing                                                                   |

| 4-23         | Microprogrammed controller and its associated microprogram control fields $\ldots$ . 139          |

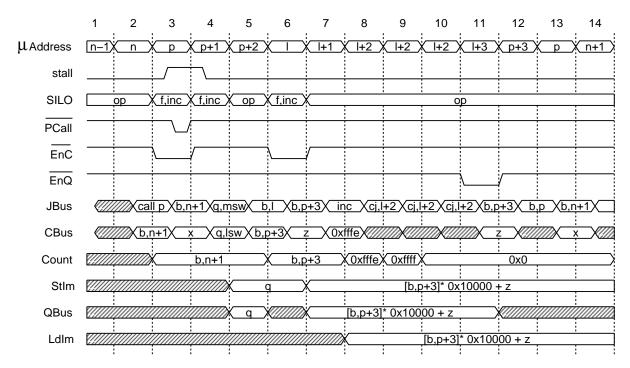

| 4-24         | A relevant sequence of operations in the microprogrammed control unit 143                         |

| 4-25         | Microprogrammed controller system timing                                                          |

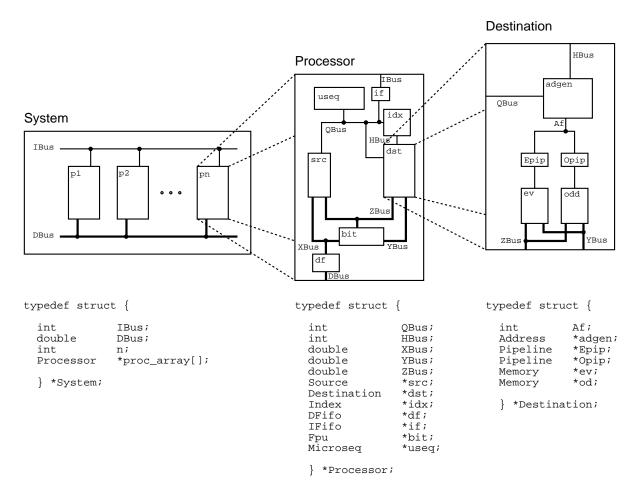

| 4-26         | Behavioral level simulation of the proposed architecture                                          |

| 4-27         | Modular hardware representation of the numerical engine and its corresponding                     |

|              | software data structures                                                                          |

| A-1         | Microcode assembler source for the evaluation of $e^x$    | . 162 |

|-------------|-----------------------------------------------------------|-------|

| <b>B-</b> 1 | The SIMLAB emulation environment                          | . 164 |

| B-2         | A Typical SIMLAB session                                  | . 165 |

| B-3         | Architectural description file used in the SIMLAB session | . 167 |

# List of Tables

| 2-1         | $Percentage \ of \ misses \ using \ column \ matching \ for \ sparse \ matrix \ decomposition \ . \ .$ | 32           |

|-------------|--------------------------------------------------------------------------------------------------------|--------------|

| 2-2         | Achievable interleaving hit ratios                                                                     | 36           |

| 2-3         | Effectiveness of reordering the rows with respect to column indices for interleaving                   | 37           |

| 2-4         | Comparison of different partitioning schemes                                                           | 46           |

| 2-5         | Comparison of different scheduling schemes                                                             | 52           |

| 2-6         | OSA overheads                                                                                          | 56           |

| 2-7         | OSA versus Sparse 1.3b                                                                                 | 58           |

| 2-8         | Influence of static column misses on the performance of the OSA-based archi-                           |              |

|             | tecture and algorithm                                                                                  | 61           |

| 2-9         | Comparison of $O^2SA$ -based and $OSA$ -based sparse matrix hardware accelerators                      | 67           |

| 2-10        | Validation of the task model in an IBM RS6000/540 workstation $\ldots \ldots \ldots$                   | 73           |

| 2-11        | Experiments on the PACE hardware                                                                       | 74           |

| 2-12        | Validation of the task model for the proposed architecture                                             | 74           |

| 3-1         | Comparison of predicted Numerical Engine performance for device evaluation                             |              |

|             | and stamping with task replication and with data transmission (shmem) $\ldots$ .                       | 94           |

| 4-1         | Index memory subsystem switching characteristics and timing requirements                               | 123          |

| 4-2         | Destination memory subsystem switching characteristics and timing requirements                         | 1 <b>3</b> 4 |

| 4-3         | Network interface system switching characteristics and timing requirements                             | 138          |

| 4-4         | Microprogrammed controller switching characteristics and timing requirements                           | 145          |

| 4-5         | Sparse matrix factorization times                                                                      | 150          |

| 4-6         | Sparse matrix factorization performance (MFlops)                                                       | 151          |

| <b>A-</b> 1 | Computation of $e^x$ on a FPU with concurrent ALU and MPY                                              | 161          |

# Introduction

Many physical systems can be modeled by large sparse systems of differential equations. Ordinary differential equations (ODE's) are often used to model time varying discrete systems such as electric circuits, or to predict the motion of planets or other bodies in space. Partial differential equations (PDE's) are used to model the space and time variation of continuous systems such as fluid and heat flow and electron transport in semiconductors. Most of the time for the numerical solution of differential equations is spent evaluating non-linearities and solving a sparse set of linear equations.

### **1.1 Thesis Contributions**

In order to efficiently evaluate the non-linearities and solve the sparse set of linear equations associated with the numerical solution of differential equations, this thesis describes the development of the Numerical Engine, a special purpose parallel processor that would take advantage of specialized hardware and software precompilation techniques in order to accelerate the solution of sparse sets of linear equations. Even though the techniques discussed in this thesis can be extended to the numerical solution of differential equations in general, it is focused on the simulation of electrical circuits, a specially challenging problem due to its unstructured nature.

In order to demonstrate the practical utilization of the Numerical Engine, we developed a modified version of a circuit simulation program, SIMLAB. Most of the computation time spent during the execution of SIMLAB is split between the assembling of sparse circuit equations, and their solution using sparse matrix techniques.

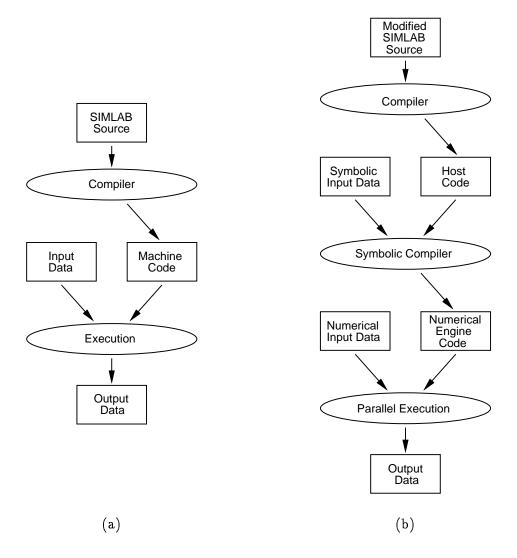

One important characteristic of these computations is that several iterations are executed with different numerical values but the sparse structure of the equations and the connectivity of the circuit is kept static. We can take advantage of this fact by executing a *symbolic compilation* that generates addressing clues, partitions the matrix and device data, schedules the internal tasks for each individual processor, and schedules the interprocessor communication sequence for the target multiprocessor system. Figure 1-1(a) depicts the traditional SIMLAB flow while the symbolic compilation step for multiprocessor execution on the Numerical Engine is introduced in Figure 1-1(b).

FIGURE 1-1: Introducing a symbolic precompilation step for SIMLAB

The major contributions of this thesis in order to speed up the parallel execution of the matrix assembly and sparse matrix decomposition tasks are:

• The  $O^2SA$  technique, which combines scheduling and storage allocation algorithms to enhance the processor efficiency. The essence of this technique is to keep an active data subset, necessary to achieve a high degree of concurrency in the sparse matrix factorization, in a small, fast memory tightly coupled with the floating point unit. Section 2.5 further discusses how to use this technique to substantially increase the factorization speed.

- Exploit the properties of sparse matrices and scattered arrays to efficiently use memory interleaving as a general technique that increases the processor-memory communication bandwidth. These properties are further discussed in Section 2.2.1.

- $O(V \log V)$  scheduling heuristics to efficiently solve sparse matrix factorization on several pipelined processors connected through a high speed bus. The fast scheduler is able to exploit the underlying hardware characteristics such as interleaving, pipelining, static column misses in DRAMs, bus conflicts, etc. A detailed discussion of the scheduling schemes proposed is presented in Section 2.3.

- Software techniques for the parallel device evaluation and parallel stamping of device contributions, in order to assemble the sparse set of equations representing the circuit behavior. Even though these techniques are fairly general and can be used in any distributed memory multiprocessor system, they have been specially tailored for the Numerical Engine. A detailed description of these techniques is available in Chapter 3.

- Specialized datapath and control in each Numerical Engine processor that permits the execution of several tasks per clock cycle. These tasks include multiple memory access, concurrent floating point and address generation operations, conditional branching, and loop control. The processor architecture is discussed in detail in Chapter 4.

In order to introduce the reader to the thesis material, the next section provides an overview of the numerical solution of differential equations.

### **1.2** Numerical Solution of Differential Equations

Numerical techniques for solving differential equations often discretize time or space (or both) to reduce the differential problem to a sequence of large, usually non-linear, algebraic systems. These systems, in turn, are solved by an iterative technique, such as the Newton-Raphson method [Press92] that involves linearizing the non-linearities, and then solving the linearized system of equations.

The evaluation of the non-linearities in a system of n equations in n unknowns, in the form of a dense matrix A, takes  $O(n^2)$  operations; the solution of the linearized system takes  $O(n^3)$ operations. These operations would be prohibitively expensive for systems with more than a few hundred discrete elements. In many cases, however, the sparse connectivity of the discrete elements causes most of the entries in the matrix A to be zero, and only a small percentage (usually less than 1%) need to be stored and operated on. The matrix A is said to be sparse, and by exploiting its sparsity the solution can be found in a tiny fraction of  $n^3$  operations. Also, the cost of assembling the matrix A is reduced in many cases to O(nonzeros).

The simulation of electric circuits is a good example of sparse matrix usage. In the modified version of SIMLAB[Lumsdaine90] (a circuit simulation program similar to SPICE[Nagel75]) used

in this thesis, each node voltage not connected to an independent voltage source is represented by one unknown and the matrix has a non-zero entry  $a_{ij}$  only if there is a circuit element connecting node *i* and node *j*. For example, the matrix *iir12*, depicted in Figure 1-2, was created during the transient simulation of the first and the second stages of an infinite impulse response digital filter. *iir12* has 7,310 equations and after the decomposition it has only 153,858 non-zero elements, corresponding to a nonzero density of 0.28%.

FIGURE 1-2: Sparse matrix created during the simulation of the first and second stages of an infinite impulse response digital filter

For PDE's, the spatial discretization of the problem in a grid naturally leads to sparse matrices. Finite difference methods will often generate regular sparse matrices given they are often linked with structured grids, while finite element methods will tend to generate an irregular non-zero pattern due to the lack of grid structure.

An important issue in the numerical solution of differential equations is the method used for solving the linear set of equations. Direct methods, like LU (lower-upper) decomposition, are able to solve the system in a fixed and finite number of steps, but are often very computationally expensive and require large amounts of memory. Indirect or iterative methods, like the Gauss-Seidel relaxation [Golub89], produce an infinite sequence of approximate answers that may or may not converge to the correct answer. If the proper conditions on the matrix A are satisfied, which is usually the case in many computational fluid dynamics problems, iterative methods will often compute a solution within a defined error margin in a fraction of the time spent by direct methods and typically will not require as much memory. However, we are particularly interested in the solution of sparse matrices related to circuit simulation, which many times exhibit poor characteristics for an iterative solution. Most commercially available circuit simulation programs available today rely on direct methods for sparse matrix solution.

Given these constraints, this thesis focuses on direct methods, and more specifically, focuses on LU decomposition, which in almost all cases is able to compute the correct solution, if one exists.

This thesis focuses on hardware and software techniques for the efficient factorization of sparse matrices and the parallel evaluation of non-linearities in an electrical circuit. The next two sections provide a brief introduction and present some background material on these topics.

### **1.3** Parallel Sparse Matrix Decomposition

The major difficulty associated with LU decomposition is its superlinear time complexity the solver tends to dominate the simulation time for large problems. This difficulty, along with the fact that most circuit simulators contain in their core a sparse matrix package that performs LU decomposition, explains the great interest in exploiting the speed of parallel and pipelined machines in order to accelerate the algorithm execution. This task is difficult due to the irregular structure of most sparse matrices associated with electrical circuits, which demands a very complex sequence of instructions and data access. Many techniques are reported in the literature to overcome these difficulties. In the following sections, we will briefly discuss *reordering, storage organization* and *scheduling*.

#### 1.3.1 Reordering

One aspect that makes the utilization of LU decomposition on a sparse matrix difficult is that even though a given element  $a_{ij}$  is zero initially, some operations can make  $a_{ij}$  non-zero during the decomposition. The new non-zero element is usually referred to as a *fill-in*. The reordering of the rows and columns of a matrix can strongly affect the number of fill-ins, and consequently the computational cost of the LU decomposition [Duff86].

Reordering is an operation that could be performed on the symbolic structure to obtain a minimum number of fill-ins. This problem has been shown to be "NP complete" [Rose78, Yannakakis81]. Many heuristics have been proposed, but the Markowitz [Markowitz57] reordering method is generally preferred since it produces on average no more than 5% more fill-ins that the best of the other methods, but takes much less time. It is a greedy strategy that tries to minimize the number of fill-ins that can occur at each step. Empirical results show that Markowitz reordering usually takes between one and two orders of magnitude more time than the actual numerical decomposition. For this reason, most sparse matrix implementations that do not require numerical pivoting perform Markowitz reordering on symbolic data only once in the beginning of the program execution.

In a parallel processor, the objective of the ordering algorithm should be the reduction of the completion time for the decomposition, which is not necessarily the ordering with the smallest number of operations. A good figure of merit for a reordering algorithm in a multiprocessor

system is the minimum number of steps required to compute the solution given an infinite number of computational resources. Several ordering algorithms have been proposed which attempt to minimize the number of steps without increasing substantially the total number of operations [Huang79, Smart89, Chang88].

#### 1.3.2 Storage Organization

Early versions of sparse matrix codes used linked list structures to represent the non-zero elements in the matrix. Given a matrix element  $a_{kj}$  (let us call it *source*), in order to perform an operation like  $a_{ij} = a_{ij} - \frac{a_{ik}}{a_{kk}} a_{kj}$ , it was necessary to traverse the linked list of row *i*, find the matching element  $a_{ij}$ , and then perform the arithmetic operation. Since these type operations dominate the LU factorization time, the slow matching process makes the entire code very slow. Even worse, the irregular access time of the elements made pipelining very inefficient.

The Scatter-Gather approach starts by scattering the elements of a destination row i into a vector of size n. Computers with pipelined indirect addressing could then perform the sourcedestination match in constant time. After all the updates to row i are finished, the elements are gathered back in a dense vector. This technique has been used in the YSMP code [Eisenstat77]. One of the disadvantages of this approach is the Scatter-Gather overhead, which is O(nonzeros). However, the major problem with this technique is that its extension to a multiprocessor environment limits the available parallelism too much, as we shall demonstrate in Section 2.4.

Stager [Stager87] proposed the enumeration of all elemental operations and addresses required for the factorization. Even thought this approach can fully exploit pipelining, the excessive memory requirement makes it infeasible for large matrices, as the number of operations grow superlinearly with the size of the matrix.

Sadayappan [Sadayappan89] studied the implementation of the sparse matrix factorization by Overlap-Scattering. All destination rows are scattered in memory, allowing a sourcedestination match of any element in constant time, just like in the Scatter-Gather approach, but no scatter and gather operations are required. In practice, if independent scatter-vectors of size n are used, the total space required would be prohibitive  $(O(n^2))$ . Fortunately, the sparsity of the rows can be exploited to share the memory efficiently, by overlapping them in such a way that the non-zeros of one row would *fill-up* the nonused elements of another. The rows are placed in scattered form into a single linear array, with different origins, such that no two rows have a non-zero in the same location in the array. During the update operation, the matching target address is computed with simple addition. Then, data from the target row is read, processed and written back to the same memory location.

Perhaps the most significant drawback in the usage of overlapped-scattered arrays is that each elemental update operation requires two accesses to a large memory that stores the entire matrix. This thesis proposes a novel technique that combines sophisticated scheduling and storage allocation algorithms by keeping only a selected set of *active* overlapped-scattered rows in a small, fast access memory in order to further enhance the processor speed. We shall refer to this allocation structure as an *Overlapped-overlapped Scattered Array* ( $O^2SA$ ). This technique is specially relevant when applied to modern computers, as the overall performance of these systems is strongly linked with the proper cache utilization.

In Section 2.4 we intend to discuss the overhead involved in using the overlap-scatter structure, and how special purpose hardware can be built in order to speed up the data access if the matrix is stored in the overlap-scattered form. Section 2.5 discusses in detail the  $O^2SA$ structure, and also discusses a processor architecture designed to take advantage of  $O^2SA$  in order to further accelerate the matrix factorization.

#### 1.3.3 Scheduling

In order to improve the utilization of a multiprocessor (or pipelined) system, a good scheduling algorithm is necessary to *choose* among the possible operations so that the most critical is executed first. The scheduling problem has been shown to be NP-complete and several heuristics have been proposed to make it computationally feasible for large problems.

Wing and Huang [Wing80] modeled the sparse matrix factorization by an acyclic directed graph in which nodes represent a task, in this case an elemental arithmetic operations applied to the elements of A, and the arcs represent the precedence relations that exist among the operations in the factorization process. They applied Hu's [Hu61] level scheduling strategy and found that the speed-up using parallel processing is proportional to the number of processors when it is ten to twenty percent of n. The major problem with their model is that the scheduling is associated with the enumeration of all elemental operations, a requirement that makes it infeasible for large matrices. As a side aspect, their model does not take into account interprocessor communication, and the different times consumed by different arithmetic operations.

Sadayappan and Visvanathan [Sadayappan88] treat the problem at differents levels of granularity. If individual tasks are row operations, then the task graph is referred to as a medium-grained model, while choosing the tasks to be elementary arithmetic operations results in a so called fine-grained model. They implemented a parallel sparse matrix solver in a shared memory multiprocessor and report that the medium-grained approach is consistently superior for large matrices due to lower operand access costs and better vectorization potential. The greedy heuristic used in Sadayappan's work tries to schedule tasks as soon as they become enabled. Even though this simple scheduling can be executed very fast, its results are quite poor since the greedy scheduling mechanism lacks the information about the *priority* of the execution of certain critical tasks.

Trotter and Agrawal [Trotter90a] suggested a level-based approach, in which all tasks of a certain level of a task graph would be executed, and then the computation would proceed in the next level. The scheduling results are not as good as the greedy-based approach because at each level many processors may stay idle. This happens because one processor is not permitted

to start the computations at the next level until all the other processors had finished the computations at the present level.

Several algorithms based on critical path scheduling are reported in the literature. In this scheme, the first scheduled tasks are in the critical path. Next, each branch is analyzed and the local critical path is scheduled in a recursive fashion. Even though this scheme produces results that are consistently better than level scheduling, the time complexity of this algorithm is O(E(V + E)) where E represents the number of edges and V the number of vertices in the task graph. For large matrices, the schedule time using this scheme becomes prohibitive.

We presented an O(VlogV) scheduling heuristic based upon the measure of the remaining completion time [Telichevesky91b]. The resulting schedules are consistently better than the level-based and greedy heuristics without a substantial penalty in the execution time. We will further discuss this scheduling heuristic and present simulation results in Section 2.3.

### **1.4 Parallel Circuit Simulation**

In order to accelerate the circuit simulation, the parallel assembly of the network equations representing the behavior of the circuit is as important as the fast parallel sparse matrix decomposition. The parallel assembly of the equations consists of evaluating the device models and adding or *stamping* their contributions to formulate the equations.

For example, let us consider a circuit simulator like SIMLAB. Each timestep in a transient analysis involves a Newton-Raphson iteration in which a voltage vector  $v^k$  can be computed iteratively by evaluating the non-linearities and solving a sparse set of linear equations of the form:

$$J_F(v^k)(v^k - v^{k-1}) = -f(v^k)$$

(1.1)

where  $J_F(v^k)$  is referred to as the Jacobian matrix that consists of the partial derivatives of the components of the charge/current equations with respect to the components of  $v^k$ , and  $-f(v^k)$ , the right-hand-side vector, consists of the contributions of the current and charge balance to the error in the approximation of the iterate  $v^k$ . The determination of the terminal currents and charges and their derivatives in respect with the terminal voltages for every device instance in the circuit is usually referred to as model or device evaluation. The sum of these contributions into the Jacobian matrix entries and into the right-hand-side vector in order to assemble the network equations is usually called stamping.

In order to achieve high efficiency for the evaluation and stamping tasks, it is necessary to consider them both at processor level and in the context of multiprocessing.

A large circuit often has thousands of circuit element instances. The model evaluation can be executed locally in each processor, so that we could simultaneously evaluate several elements. In order to quickly execute these tasks each processor of the Numerical Engine contains several functional units controlled by a single, wide instruction stream able to initiate several operations per clock cycle. Hand programming such a machine is not a trivial task, and building a simplified compiler that makes this job easier might be even more difficult. Even though some background work in this field is presented in [Ellis85], and we performed some preliminary studies in order to implement such compiler, the task was abandoned. Consequently, the parallel model evaluation was only simulated at the behavioral level, discussed in detail in Section 4.3.1.

Stamping requires a more complex analysis in the context of multiprocessing. Sadayappan and Visvanathan [Sadayappan88] describe this process as a *lock-synchronized parallel loop*. They present a theoretical analysis and compare with measured speedups on a shared memory multiprocessor. However, the implementation becomes inefficient if the number of parallel processors is larger than six. We intend to further discuss this problem and present a detailed account of our implementation on the Numerical Engine (a distributed memory system) in Chapter 3.

The computation of transcendental functions is a very time consuming task in non-linear evaluation. A mathematical library of transcendental functions based on the fast evaluation of Chebyshev polynomials [Clenshaw63, Clenshaw62] was hand-coded for the Numerical Engine architecture proposed in Chapter 4. A combination of operation reordering, clever register allocation and multiple memory access was used to achieve a high utilization of the floating point hardware. We shall further discuss these techniques in Appendix A.

### **1.5 Numerical Engine Architecture**

The factorization of sparse matrices is a very inefficient operation on general purpose computers due to the difficult access to sparse matrix elements. The difficulty in accessing sparse matrix elements is partly due to the address generation complexity, and partly due to the large bandwidth requirements between the main memory and the floating point unit. The end result is a poor utilization of the floating point resources, specially in state-of-the-art heavily pipelined architectures. For instance, experimental results show that the average floating point unit utilization of an AXP ALPHA computer is around 2% for sparse matrix factorization. A detailed discussion of the experimental results is provided in Section 4.4.

The Numerical Engine architecture overcomes the difficulties mentioned above by using specialized hardware and the combination of scheduling and storage algorithms for the fast parallel factorization of sparse matrices. The primary objective of the architecture development was the design of a multicomputer containing processing elements with added hardware support for fast sparse execution of operations of the type  $a_{ij} = a_{ij} - a_{ik} \times a_{kj}$ , which are the most frequent operations in matrix decomposition. In order to achieve its primary objective, each processing element has multiple interleaved memories to supply data at high rates for the floating point unit, support for the concurrent generation of addresses and writeback, and a simple but fast pipeline interlock mechanism. In order to provide high speed control with the smallest possible latency, the controller is a very simple microprogrammed unit, containing a very wide microinstruction memory tightly coupled with the datapath. The Numerical Engine performance for sparse matrix decomposition has been tested by a detailed register transfer level (RTL) simulation, using a hand microcoded sparse matrix package for a single processor. The results indicate that a single Numerical Engine processor could solve sparse matrices at a sustained rate of 73 MFlops, or 73% utilization of the floating point unit. These results are further discussed in Section 4.4.

The Numerical Engine is also expected to perform the device evaluation and stamping tasks described briefly in Section 1.4 and discussed in detail in Chapter 3 with a high degree of floating point unit utilization. Even though these tasks have not been simulated in detail using RTL simulation due to the extreme difficulty in writing its microcode, it seems that they could also achieve high performance. This theory is supported by the high degree of floating point unit utilization, 89% or 89 MFlops, achieved in the RTL simulation of the evaluation of the transcendental function  $e^x$ , described in detail in the Appendix A.

A detailed description of the Numerical Engine architecture is presented in Chapter 4.

#### 1.5.1 Related Work

Gyurcsik and Pederson [Gyurcsik85] have designed, assembled and tested a prototype of an attached processor for an IBM-PC computer for MOS model evaluation. The system uses a table-based approach for the fast evaluation of the contributions of MOS transistors to the assembly of the network equations.

Ginosar and Jacobson [Ginosar85] proposed a VLSI architecture for circuit simulation based on waveform-relaxation. They proposed several specialized building blocks that would perform concurrently different tasks required for the implementation of the waveform-relaxation algorithm.

Lewis [Lewis86] suggested the usage of a Forward-Euler integration method for avoiding the solution of a sparse system of network equations in circuit simulation and proposed a specialized hardware for matrix multiplication and table-based evaluation of the device contributions. The shortcoming of the Forward-Euler integration method is that it requires very small timesteps to ensure the stability of the solution.

Nakata, Tanabe, Onozuka, Kurobe and Koike [Nakata87] used a relaxation method for circuit simulation, dividing the circuit to be simulated into several *modules* for independent evaluation on a specialized parallel computer.

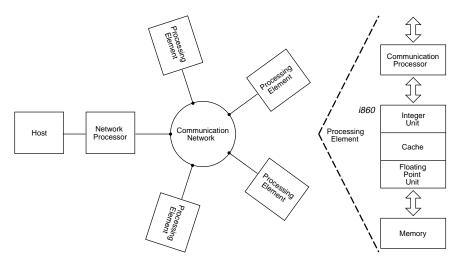

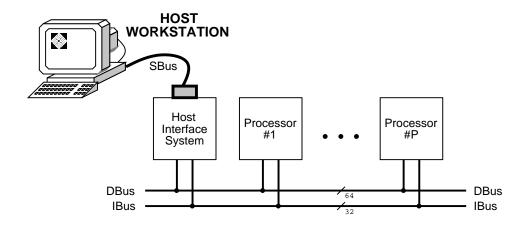

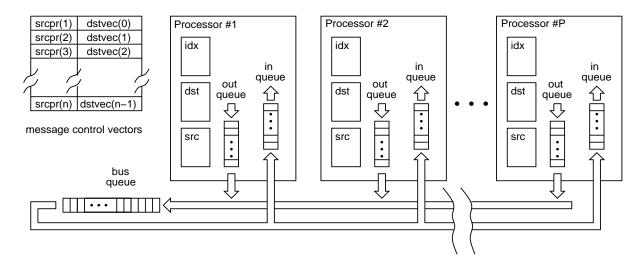

Agrawal and Trotter [Agrawal92] have designed, assembled and tested a prototype machine, named PACE (Parallel Architecture for Circuit Evaluation), which consists of four *Intel i860* [Intel90] microprocessors connected by a wide high speed bus. The PACE hardware is intended for circuit simulation using a direct method solver. The PACE partitioning and scheduling heuristics for sparse matrix decomposition are the same as the techniques presented in Chapter 2 of this thesis.

FIGURE 1-3: General architecture of the PACE

Figure 1-3 gives a block diagram of the machine. It consists of several processing elements (PEs) and a communication network (CN) controlled by a network processor (NP) and a host processor. The prototype PACE is a wire-wrapped circuit board that connects to the backplane of a VME SUN workstation. The network processor provides an interface to the host and controls the PEs and the communication network by sequencing the communication transactions. Each of the four PEs has a communication processor that interfaces to the communication network, an integer unit that is responsible for address calculation, a floating point unit, cache, and a memory system to hold the bulk of matrix data.

Performance measurements on PACE, using matrices generated during the simulation of VLSI circuits, demonstrate the effectiveness of the partitioning and scheduling heuristics suggested in this thesis. A detailed discussion of the PACE performance is provided in Section 2.6.2.

## **1.6** Thesis Outline

As discussed before, this thesis presents hardware and software techniques for the fast numerical solution of differential equations, with an emphasis on the fast execution of the circuit simulation algorithm. Most of the computation time in a circuit simulator is spent in the assembly of a sparse set of linearized equations that represent the circuit behavior and solving them.

Chapter 2 describes several software and hardware techniques that accelerate the solution of sparse sets of linear equations. These techniques include storage allocation methods to simplify data access, multiprocessor scheduling mechanisms, and how to exploit the locality of reference and hardware characteristics such as pipelining, main memory paged-mode access, and interleaving, in order to achieve a high degree of utilization of computational resources both at processor and at system level.

Chapter 3 describes several software techniques that accelerate the assembly of the linearized equations representing the circuit behavior in a general purpose multiprocessor environment, and are specially effective when applied to the Numerical Engine proposed in Chapter 4.

Chapter 4 provides a comprehensive description of the proposed Numerical Engine architecture, both at system and at processor level. A complete description of the interprocessor bus interface protocol and electrical specification, as well as system-wide issues such as clock generation is provided in the first section of Chapter 4. The second section presents a detailed explanation of the register-transfer-level operation and accurate timing information on the components of each individual processing element. The third section provides a description of software developed for the architectural emulation and the verification of its proper operation when executing a modified version of SIMLAB. The last section provides a comparison of the predicted performance of a single processing element with measurements taken from commercially available state-of-the-art general purpose computers.

Finally, Chapter 5 summarizes the simulation results and presents a discussion on the major contributions of this thesis, suggesting some paths for future research.

# Parallel Sparse Matrix Decomposition

A sparse system of linear algebraic equations can be written in matrix form as Ax = b, where  $A = [a_{ij}]$  is an  $n \times n$  sparse matrix of real or complex coefficients, x is the vector of nunknowns and b is the vector of n known right-hand side terms. In this work, we will assume  $a_{ij}$  are real numbers.

If  $a_{ij}$  are complex coefficients, the sparse matrix decomposition can be performed using analogous techniques. The overall pattern of matrix data access and operations, and specially its impact on computer architectures is very similar. In fact, matrices with complex elements represent a less challenging problem in terms of achieving high processor efficiency. One of the major factors that reduce the efficiency of sparse matrix computations is the bandwidth between the memory and the floating point unit. It is very difficult to design a memory system that can keep pace with the floating point unit for the predominant operation in matrix decomposition, called gaxpy [Golub89], and defined as  $a_{ij} = a_{ij} + a_{ik} \times a_{kj}$ . In sparse matrices with real coefficients, four memory accesses are required per gaxpy, and only two arithmetic operations are performed. If the coefficient are complex, eight memory accesses are required, but eight arithmetic operations are performed.

It is desirable to exploit the sparsity of some matrices, such as the large, unstructured matrices generated during circuit simulation. The most obvious reason is to avoid storing the elements that are zero in the beginning of the decomposition and will never change during the decomposition, which are called *structural zeros*. Not storing these zeros makes it much more complicated to store the other matrix elements, called *structural non-zeros*. These elements could be originally non-zeros, or they might become non-zero during the course of decomposition, and in that case they are called *fill-ins*. In the matrix examples further discussed in this chapter, the non-zeros account roughly for 0.1% to 0.7% of the elements in the corresponding dense matrix. Another advantage of not storing the structural zeros is that no time is required

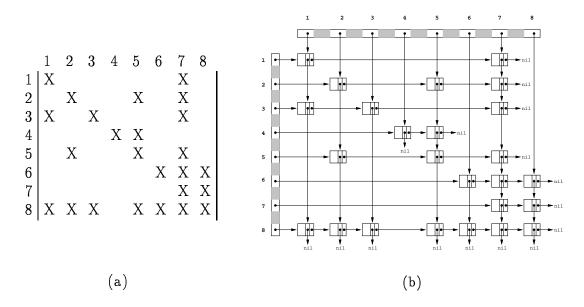

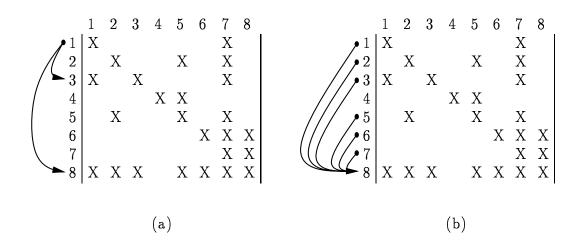

FIGURE 2-1: A sparse matrix (a) and its associated orthogonal linked list storage (b)

One way of storing the structural non-zeros is by using orthogonal linked lists, described in [Kundert86]. For example, consider the sparse matrix depicted in Figure 2-1(a) and its associated orthogonal linked list storage representation, as shown in Figure 2-1(b). In this representation, each structural non-zero element corresponds to a data structure which typically contains the numerical value  $a_{ij}$ , the row and column indices i and j, and a pair of pointers to the next data structure in the row and column. Even though simple and very flexible, this orthogonal linked lists are not very efficient when used to perform factorization. Several different storage data structures have been proposed that help to achieve faster access to matrix data, and these will be discussed later in this chapter.

As mentioned in Chapter 1, there are two classes of methods for solving systems of equations: direct methods, which are able to solve the system in a fixed and finite number of steps, and indirect or iterative methods, which produce an infinite sequence of approximate answers that may converge to the correct answer. Since we are particularly interested in the decomposition of sparse matrices for circuit simulation, iterative methods will only converge if rather strong conditions on A are satisfied.

It is often desirable to solve a system of equations with more than one right-hand side, preserving the original matrix. In circuit simulation, this technique is widely used to avoid the costly reconstruction of the Jacobian matrix in the inner loop of a Newton iteration, as described in Chapter 3. A simple modification of the original Gaussian Elimination scheme, allows the solution of various problems with varying right-hand side vectors b. This technique, called LU decomposition, is widely used in simulators and will be further discussed in Section 2.1. This work is focused on direct methods, and in particular, LU decomposition.

In this chapter, several aspects of parallel sparse matrix decomposition will be discussed. Section 2.1 introduces the basic sparse LU factorization and the column match problem related to the usage of the orthogonal linked list storage by itself. Section 2.2 will describe the Scatter-Gather approach, which solves the column match problem. Section 2.3 will introduce the readers to the extensions of the basic LU decomposition algorithm for a multicomputer environment, and will present a greedy heuristic based on a multitask graph measure called remaining completion time which empirically generates excellent multiprocessor schedulings without a substantial penalty in the execution time. Section 2.4 will describe Overlap-Scatter Arrays, and how its flexibility greatly enhances the utilization of a parallel processor when compared with the plain Scatter-Gather approach. Section 2.5 will introduce  $O^2SA$  arrays and how they can be used to exploit locality of reference within each processor without sacrificing multiprocessor performance. Section 2.5.3 also discusses how to change the scheduling mechanism to accommodate different storage organizations. Finally, Section 2.6 addresses some actual implementation issues, using an enhanced scheduler to predict the performance of serial and parallel processors.

### 2.1 Sparse LU Factorization

The LU factorization or decomposition consists of applying preserving transformations on the original matrix A, decomposing into the product of two matrices, L and U, which are respectively lower and upper triangular, as:

$$Ax = L(Ux) = Ly = b \tag{2.1}$$

Once the matrix A is factored into L and U, it is easy to solve the lower triangular problem Ly = b for y, in a process called *forward elimination*. Then, the upper triangular system Ux = y can be solved for x, in a process called *back substitution*. The decomposition can be thought as the product:

| $l_{11}$ | 0        |       | 0        | $u_{11}$ | $u_{12}$ |       | $u_{1n}$        |   | $a_{11}$                      | $a_{12}$ |     | $a_{1n}$        |

|----------|----------|-------|----------|----------|----------|-------|-----------------|---|-------------------------------|----------|-----|-----------------|

| $l_{21}$ | $l_{22}$ | • • • | 0        | 0        | $u_{22}$ | • • • | $u_{2n}$        | _ | $a_{21}$                      | $a_{22}$ | ••• | $a_{2n}$        |

| ÷        | ÷        |       | ÷        | ÷        | ÷        |       | $u_{2n}$        | _ | ÷                             | ÷        |     | :               |

| $l_{n1}$ | $l_{n2}$ |       | $l_{nn}$ | 0        | 0        |       | u <sub>nn</sub> |   | <i>a</i> <sub><i>n</i>1</sub> | $a_{n2}$ |     | a <sub>nn</sub> |

If the matrix is dense, this system has  $n^2$  equations corresponding to the elements of A, and  $n^2 + n$  unknowns, the entries of L and U. Since this is an under-determined system of equations, n elements can be chosen freely. For implementation reasons, we chose to set the diagonal elements of U to one, which is often referred to as *Crout's algorithm for LU decomposition*, with the small difference that only row-wise operations are performed. Assuming the original coefficients  $a_{ij}$  are no longer necessary, it is possible to perform all computations in place, i.e. no additional storage is required to store the LU coefficients. The upper-triangular diagonal elements  $u_{kk}$  are implicitly stored, as they are all set to  $u_{kk} = 1$ . In terms of memory usage, these are the key advantages of the LU decomposition method.

Since floating point divisions are more expensive operations than floating point adds or multiplies, another small change in the original Crout's algorithm involves computing the reciprocal of  $a_{kk}^{-1} = \frac{1}{a_{kk}}$  and storing it for future use. The original value  $a_{kk}$  is discarded.

Given A, a non-singular sparse matrix, Algorithm 2.1 can be used to solve the system of equations Ax = b. This algorithm is called *Source-row directed* because at each LU decomposition step, some row k is picked to be used as a *source*, i.e. to update the rows i underneath it. The rows i, updated by row k, are called *destination*, or *target* rows. If it is necessary to solve for multiple  $b^{(m)}$ , multiple forward eliminations and back substitutions are executed, but only one LU decomposition. The double loop marked "Update" consumes most of the time during the algorithm execution.

Algorithm 2.1 exploits the sparsity of the matrix to reduce the number of operations required to solve the system of equations. If a sparse matrix problem is solved as a dense matrix problem,  $O(n^3)$  operations would be required. The number of operations necessary when the matrix sparsity is exploited decreases to  $O(n^{\alpha})$ , where  $\alpha$  is a factor which depends on the structure of the matrix.  $\alpha$  is 1.5 for a grid, and probably smaller for circuit problems, but difficult to determine exactly. The matrix sparsity is represented in Algorithm 2.1 by the operator **foreach**, which visits all the elements on a list of structural non-zeros. Using the data structure shown in Figure 2-1(b), the access of the desired non-zero elements consists of visiting the next element in the linked list, and is reasonably trivial for all **foreach** cases, except for the element marked  $a_{ii}^*$  in the update loop.

Consider, for example, the execution of the update loop in Algorithm 2.1, and more specifically, the operation  $a_{87} = a_{87} - a_{81} \times a_{17}$  during the factorization of the example matrix depicted in Figure 2-1. The element  $a_{ik} = a_{81}$  is naturally accessed by visiting the next element in the first column list during the execution of the outer **foreach** loop. The element  $a_{kj} = a_{17}$  is also easily accessed by visiting the next element in the first row during the execution of the inner **foreach** loop. However, there is no obvious way of accessing directly  $a_{ij}^* = a_{87}$  with this data structure. In order to reach element  $a_{87}$  it is necessary to traverse the linked list binding the element is reached. An inefficient approach to this search, often referred as *column matching*, can substantially degrade the performance of sparse matrix factorization algorithms.

In order to quantify the costs of column matching, when an element  $a_{ij}$  is read, but its column index does not match the desired index, we refer to this as a *miss*, because an entry is read but not used. Table 2-1 summarizes the number of *gaxpys* and misses for a number of test matrices derived from the circuit simulation of real VLSI circuits. *dram* is a 2806 × 2806

```

Algorithm 2.1 (Modified Source-row Directed Form of Crout's Algorithm).

k = 1

while k \leq n {

/* LU Decomposition */

a_{kk}^{-1} = rac{1}{a_{kk}}

for each j > k such that a_{kj} \neq 0

a_{kj} = a_{kk}^{-1} \times a_{kj}

/* Normalize */

for each i > k such that a_{ik} \neq 0

for each j > k such that a_{kj} \neq 0

a_{ij}^* = a_{ij}^* - a_{ik} \times a_{kj}

/* Update */

k = k + 1

}

k = 1

while k \leq n {

/* Forward Elimination */

y_k = b_k^{(m)}

for each j < k such that a_{kj} \neq 0

y_{k} = y_{k} - a_{kj} \times y_{j}y_{k} = a_{kk}^{-1} \times y_{k}

k = k + 1

}

k = n

while k \ge 1 {

/* Back Substitution */

x_k = y_k

\mathbf{foreach}\ j>k \text{ such that } a_{kj}\neq 0

x_k = x_k - a_{kj} \times x_j

k = k + 1

}

```

matrix representing a subsection of a dynamic memory chip. feb is part of a bitonic sorter chip. mesh represents the solution of a two-dimensional Poisson problem on a  $32 \times 32$  grid. The other matrices are derived from digital signal processing circuits. The table also lists, in the sixth column, the percentage of wasted reads. In extreme cases, the percentage of these misses can be as high as 99%. In other words, if the column matching is performed as suggested in the previous paragraph, the decomposition time would be a hundred times slower than necessary. It should be noted that in earlier machines, read overhead was small compared with the time required to perform a floating point operation, making misses less significant. For this reason, older versions of circuit simulators like SPICE [Nagel75] used only a orthogonal linked list storage. However, in modern workstations and supercomputers, the overhead is much larger than the time necessary for a floating point operation, making avoiding misses much more important.

Next section will describe the Scatter-Gather approach, which provides an elegant solution

| matrix | n          | nonzeros    | gaxpys          | misses           | $\operatorname{misses}(\%)$ | total            |

|--------|------------|-------------|-----------------|------------------|-----------------------------|------------------|

| dram   | 2,806      | 55,706      | $908,\!129$     | 3,081,412        | 77.24                       | 3,989,541        |

| feb    | $10,\!060$ | $136,\!486$ | $291,\!230$     | $26,\!271,\!225$ | 98.90                       | $26,\!562,\!455$ |

| mesh   | 961        | $28,\!881$  | $325,\!920$     | $76,\!604$       | 19.03                       | $402,\!524$      |

| iir12  | $7,\!310$  | $153,\!858$ | $1,\!734,\!954$ | $1,\!525,\!921$  | 46.79                       | $3,\!260,\!875$  |

| iir123 | $11,\!014$ | $229,\!004$ | $2,\!449,\!967$ | $2,\!522,\!306$  | 50.73                       | $4,\!972,\!273$  |

| omega  | 4,212      | $48,\!850$  | $53,\!178$      | $6,\!431,\!113$  | 99.18                       | $6,\!484,\!291$  |

| mfr    | 5,496      | $93,\!826$  | $378,\!976$     | $1,\!280,\!927$  | 77.16                       | $1,\!659,\!903$  |

| total  |            |             | $6,\!142,\!354$ | $41,\!189,\!508$ | 87.03                       | 47,331,862       |

Table 2-1: Percentage of misses using column matching for sparse matrix decomposition

to the column match problem.

## 2.2 The YSMP Scatter-Gather Approach

The Scatter-Gather approach was first introduced in the Yale Sparse Matrix Package [Eisenstat77]. The basic idea consists of adding to the sparse matrix representation an extra vector S of size n which holds the values of  $a_{ij}^*$  in Algorithm 2.1 in scattered form. Instead of traversing a linked list to match the proper column index, the value of  $a_{ij}^*$  is directly obtained as  $a_{ij}^* = S[j]$ , using indirect addressing. In order to obtain this representation, the *i*-th row is first scattered in the proper positions of the vector S, the row operation performed, and then the *i*-the row is gathered back into its previous compact representation.

Using the approach just described, the great advantages introduced by the elimination of the linked list traversal would be entirely offset by the overhead costs due to the scattering and gathering of a row before and after each inner loop of the update. A much better approach would be to move the scattering and gathering process out of the update loop, in which case each row would be scattered and gathered only once during the factorization. In order to achieve this goal, it is necessary to fundamentally change Algorithm 2.1 to a *Target-row directed* form of the sparse matrix decomposition.

Figure 2-2(a) depicts the Source-row directed nature of the Algorithm 2.1. In particular, the first execution of the update loop is highlighted, showing the first row updating rows beneath it. In general, in each update loop, a particular source row k is fixed, and used many times to update the rows beneath it.

In order to take full advantage of the Scatter-Gather mechanism, in each update double loop, a particular destination, or target row i, is fixed, and used many times to be updated by the rows above it. Figure 2-2(b) depicts the *Target-row directed* version of Crout's algorithm. In particular, the last execution of the update loop is highlighted, showing the update of the last row by other rows above it.

FIGURE 2-2: Source-row directed (a) and target-row directed (b) forms of sparse matrix decomposition

Given A, a non-singular sparse matrix, and a scatter vector S, Algorithm 2.2 can be used for the efficient LU decomposition of A. In order to solve Ax = b, the forward elimination and back substitution steps shown in Algorithm 2.1 are used without any changes. This algorithm can be slightly refined by combining the *gather* and *normalize* operations for the common elements. Even though this method is used in the actual implementation, the original form was left here for clarity. Though both algorithms represent exactly the same set of arithmetic operations, the execution in different sequential order have a great impact on the operand's access and parallelization. Later in this chapter, we shall demonstrate that both Algorithms 2.1 and 2.2 restrict the available parallelism too much.

```

Algorithm 2.2 (Scatter-gather Target-row Directed Form of Crout's Algorithm).

i = 1

while i \leq n {

/* LU Decomposition */

for each j such that a_{ij} \neq 0

/* Scatter */

S[j] = a_{ij}

for each k < i such that a_{ik} \neq 0

for each j > k such that a_{kj} \neq 0

S[j] = S[j] - a_{ik} \times a_{kj}

/* Update */

for each j such that a_{ij} \neq 0

a_{ij} = S[j]

/* Gather */

a_{ii}^{-1} = \frac{1}{a_{ii}}

\mathbf{foreach}^n j > i such that a_{ij}

eq 0

a_{ij} = a_{ii}^{-1} \times a_{ij}

/* Normalize */

i = i + 1

}

```

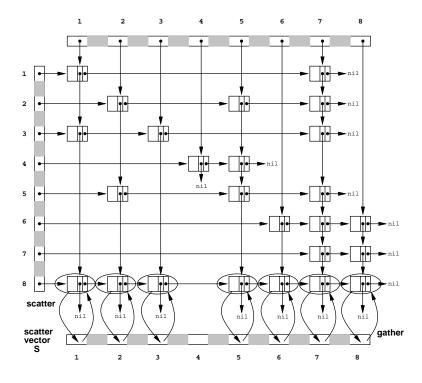

Figure 2-3 helps illustrate the whole Scatter-Gather process. Before each update loop, the elements of a particular target row are scattered into the proper position j in the S vector by traversing the linked row list and using the column index j as an address. This process, called *scattering*, is depicted in Figure 2-3 with arrows pointing to the scatter vector S. During the update loop, access to the source elements  $a_{kj}$  and the multipliers  $a_{ik}$  is naturally done by visiting the next element in the linked lists, just as described in Algorithm 2.1. The difference is that instead of traversing a linked list to reach  $a_{ij}^*$ , there is an immediate indirect access to S[j]. After all the update operations are finished, it is possible to gather back the elements of the row by traversing the linked row list and using the column index j as an address. This process, called *gathering*, is depicted in Figure 2-3 with arrows pointing from the scatter vector S back to the actual matrix elements.

The impact of scattering the destination rows has broader implications than just the simplification of the column search. Supercomputers with pipelined indirect addressing capabilities could use the Scatter-Gather algorithm and take advantage of the constant update time in order to keep the floating point arithmetic pipelines full. Another advantage of this method is that it exploits the *locality of reference* for accessing data. The destination row accesses can be done to a local cache that keeps the scatter vector S. The source row access, though accessing a large memory, is sequential, which might be an advantage for some computers.

FIGURE 2-3: Scatter-Gather LU decomposition

Another advantage of the Scatter-Gather approach, also useful in all storage mechanisms that use scattering, is the *efficient interleaving*, described in detail in the next section.

#### 2.2.1 Efficient Interleaving in Scattered Vectors

As mentioned earlier, one of the key issues for achieving high efficiency in sparse matrix computations is the design of a memory system that can keep pace with today's fastest floating point units. In order to increase the memory throughput, a possible design decision is to use faster memories, which tend to be smaller and much more expensive or, if possible, use interleaving.

Consider the memory organization shown in Figure 2-4. There are M memory modules, each one with its independent memory address registers (MAR) and memory data registers (MDR). A fast processor could issue up to M memory requests  $req_i$  during a single memory cycle if all requests are guaranteed to be directed to distinct memory modules. The address space is divided in such way that memory module i contains all addresses k such that  $i = k \mod M$ . This organization is called *M*-way interleaved memory.

FIGURE 2-4: *M*-way interleaved memory system

If memory accesses were sequential, it would be easy to achieve a high degree of efficiency in interleaving, because the data would certainly be in distinct memory banks. This is the case when accessing source row elements and column indices during the update loop in Algorithm 2.2. However, the target row elements are scattered in a random order with respect to the interleaved memory banks. For example, in a two-way interleaved memory system, the *hit ratio*, or the chance of accessing a particular target row element in a given memory bank is 50%. By multiplying the number of memory modules (2) by the *hit ratio* just described (50%), we obtain the *effective usage* of the memory system. In our example, the effective usage is 1.0, or in other words, the usage of interleaved memories is a waste, as the same results would be obtained using a non-interleaved memory system.

| matrix  | 2-way | 4-way | 8-way |

|---------|-------|-------|-------|

| dram    | 0.93  | 0.85  | 0.73  |

| feb     | 0.81  | 0.59  | 0.39  |

| mesh    | 0.96  | 0.87  | 0.77  |

| iir12   | 0.94  | 0.83  | 0.68  |

| iir123  | 0.93  | 0.82  | 0.67  |

| omega   | 0.76  | 0.53  | 0.34  |

| mfr     | 0.88  | 0.70  | 0.50  |

| Average | 0.88  | 0.74  | 0.58  |

Table 2-2: Achievable interleaving hit ratios

On the other hand, it is desirable to achieve a high degree of interleaving, specially for the memories that hold the scattered destination row. In terms of a sparse matrix solver implementation, this is particularly important because each *gaxpy* operation requires both a read and a write access cycle in the target data memory.